1.简介

本文主要介绍如何在 vivado 中创建自定义 IP 核,示例使用 vivado22.1 完成对 UART 的打包工作。

2.操作步骤

1. 在自定义 IP 核之前,要先准备写好的源码,并且应当包括相应的 top 文件。但是如果你在设计中用了官方的 IP 核又没使用 Block Design(以下简称 BD)的情况下,你需要将 IP 文件也放入准备好的文件夹中,但目前我使用这种方式并不生效,需要在 2 和 3 步骤之间重新加入 IP 核(提前加入 IP 核不仅不会生效还会让所有源码都不能正常识别),因此推荐以后的工程一律使用 BD。

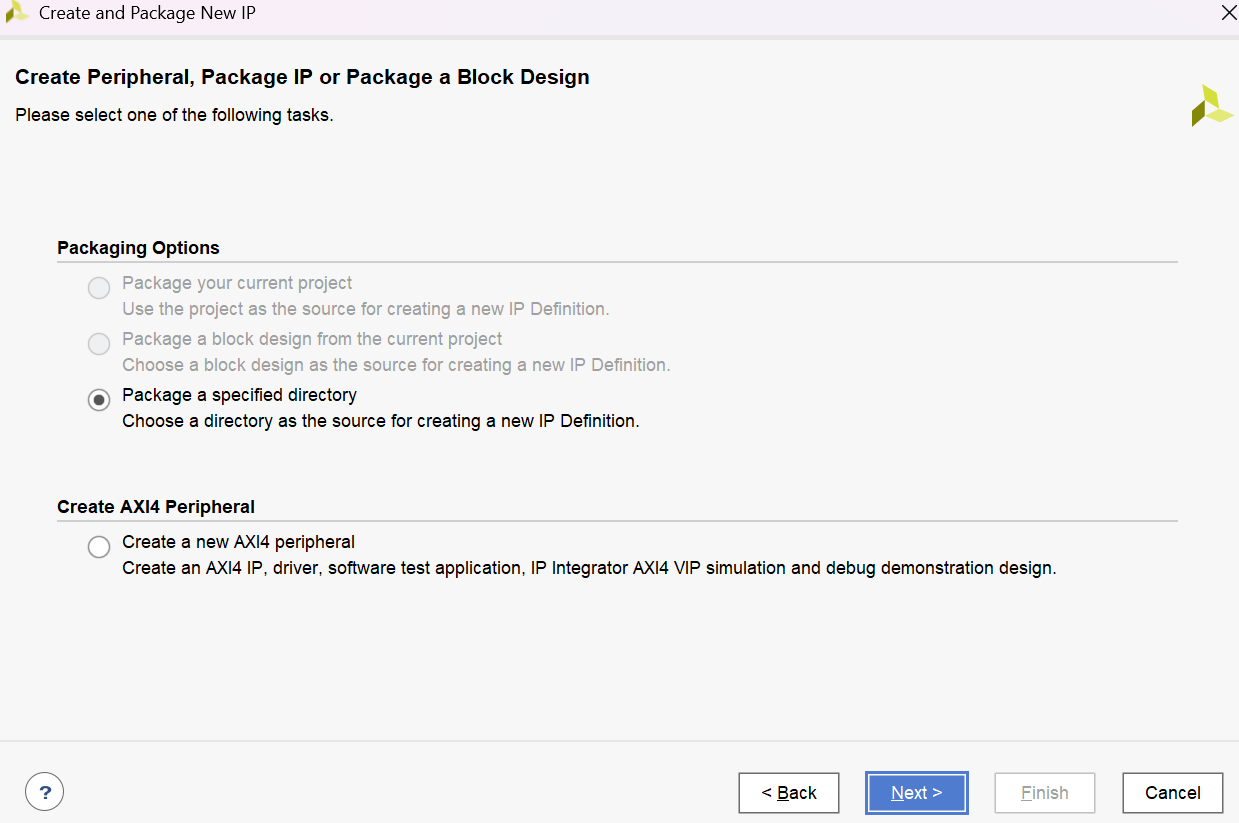

2. 新建一个空白工程,点击 tools——>Create and Package New IP 开始创建 IP

图 1

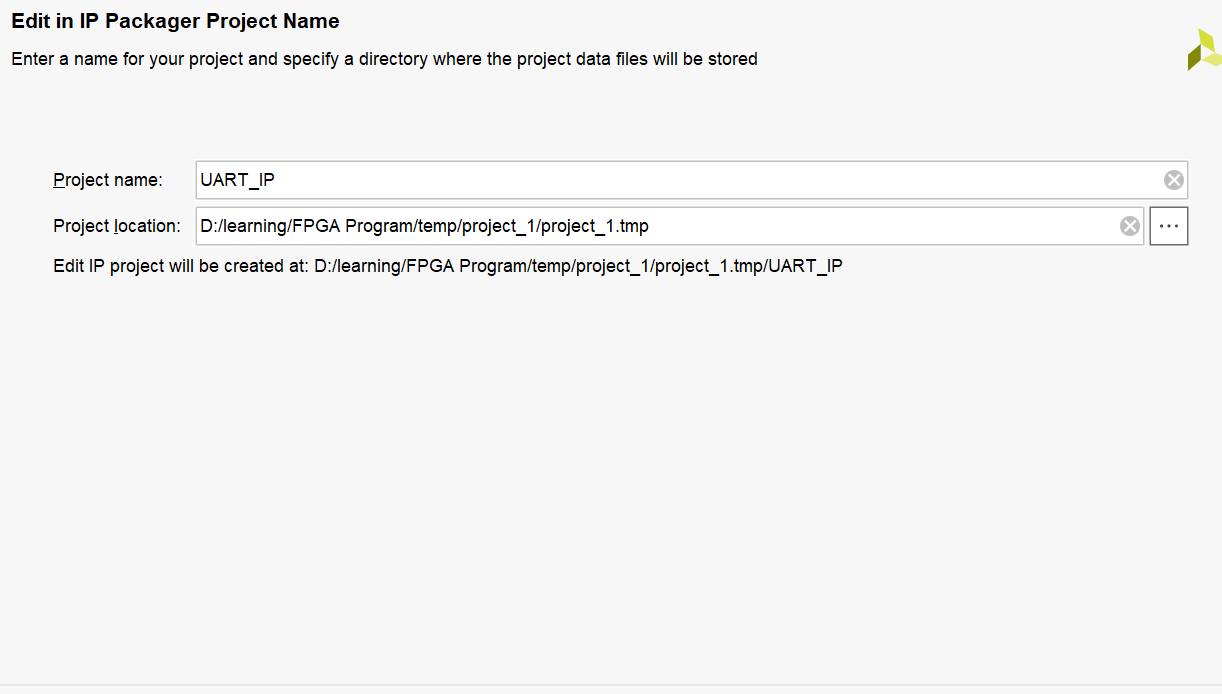

在图 2 的步骤可以改 IP 的名字:

图 2

本步对应 tcl 代码如下:

create_project project_1 {D:/learning/FPGA Program/temp/project_1} -part xc7vx485tffg1157-1

ipx::infer_core -vendor xilinx.com -library user -taxonomy /UserIP {D:/learning/FPGA IPs/temp}

ipx::edit_ip_in_project -upgrade true -name UART_IP -directory {D:/learning/FPGA\ Program/temp/project_1/project_1.tmp} {d:/learning/FPGA IPs/temp/component.xml}

ipx::current_core {d:/learning/FPGA IPs/temp/component.xml}

update_compile_order -fileset sources_13. 参数设置

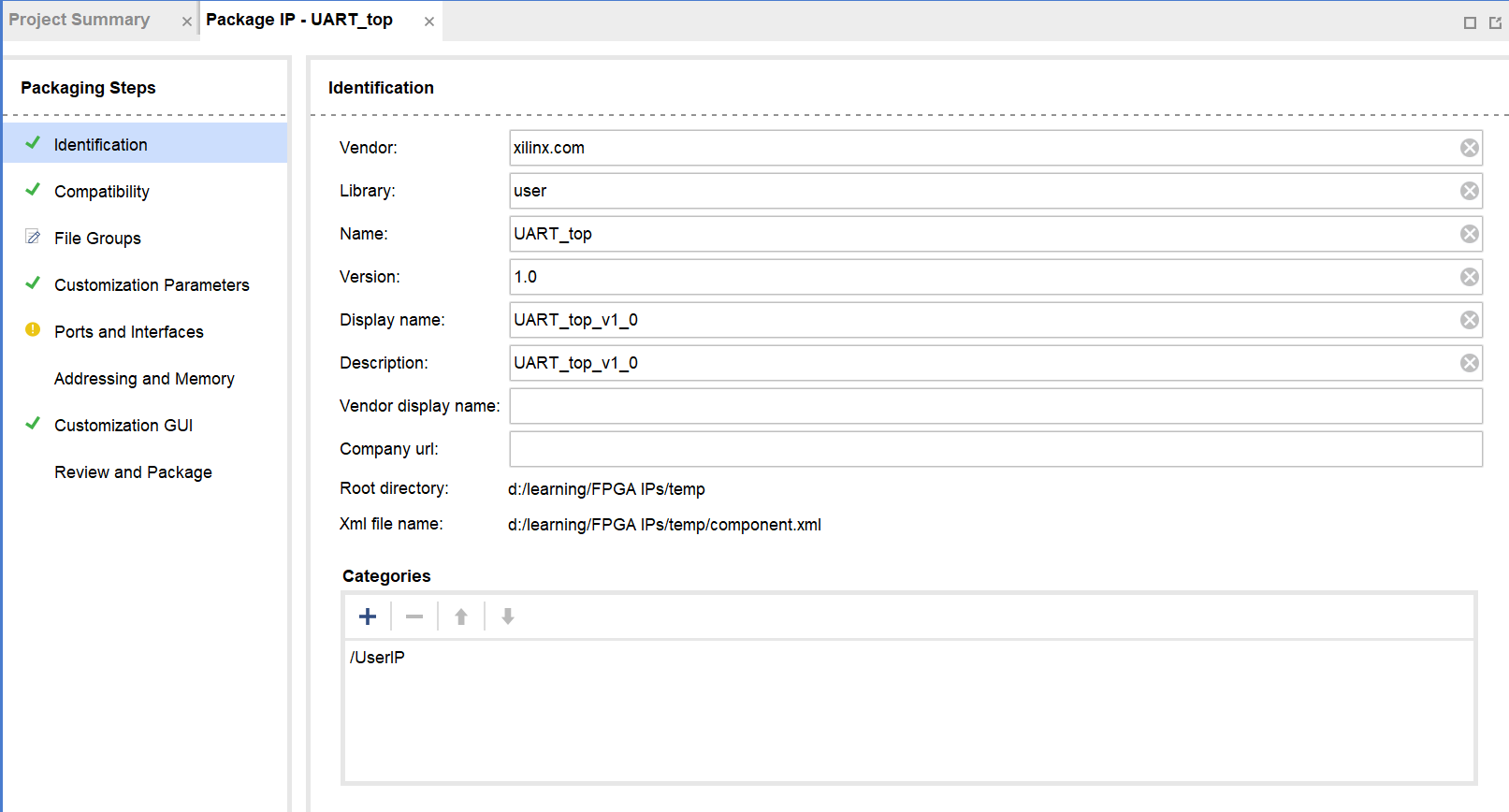

如下图所示,IP 在创建之初就已经有一些预先给好的基本信息(标识 /Identification)了。也可以对其中一些内容做想要的修改。

图 3

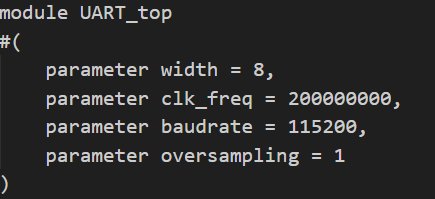

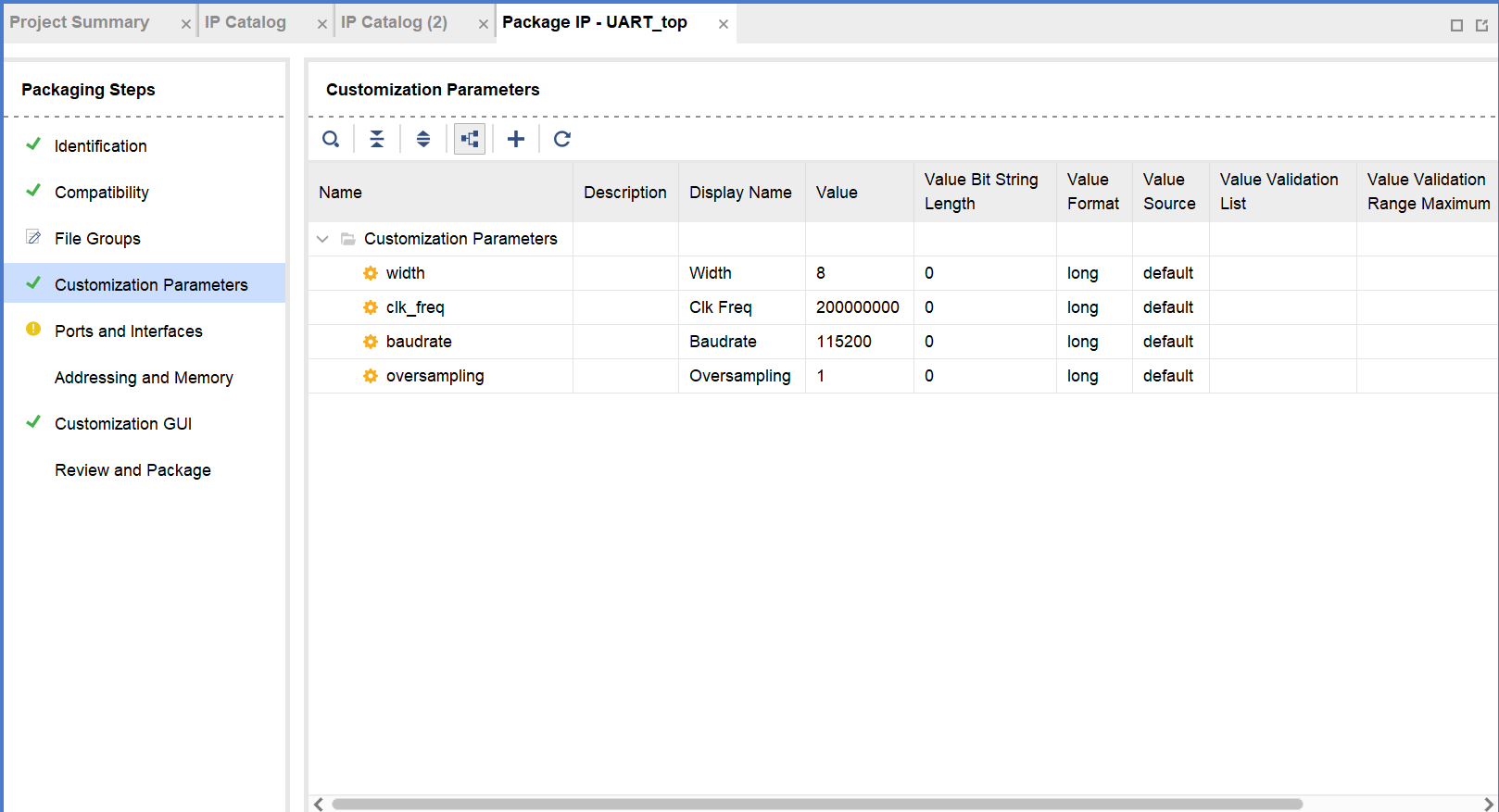

在左侧选择 Customrization Parameters 可以进入参数设置页面,这些参数一般都是由 top 文件中的 parameter 给出,由图 4 的源码中的 top 文件参数部分和图 5 对比就可以知道。

图 4

图 5

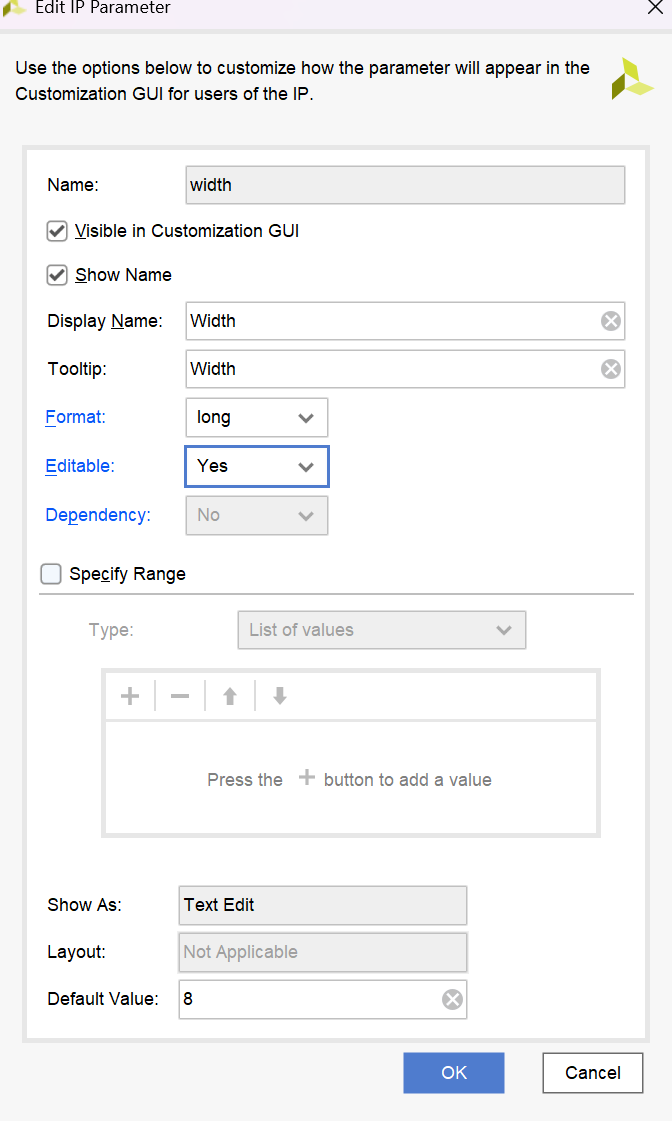

双击图 5 中的参数,可以对其做自定义修改,双击可得如图 6 所示的面板进行修改:

图 6

其中 Editable 表示该项参数的可编辑性,很多设计中该项是搭配 Specift Range 使用的,使用 Specift Range 可以让用户在使用自定义 IP 时只能选择你所提供的几种选择。值得一提的是 Editable 中有个 dependent 选项,如果你需要提供可关闭的接口时,要使用 dependent 选项对某些相关联的接口做相应的调整。

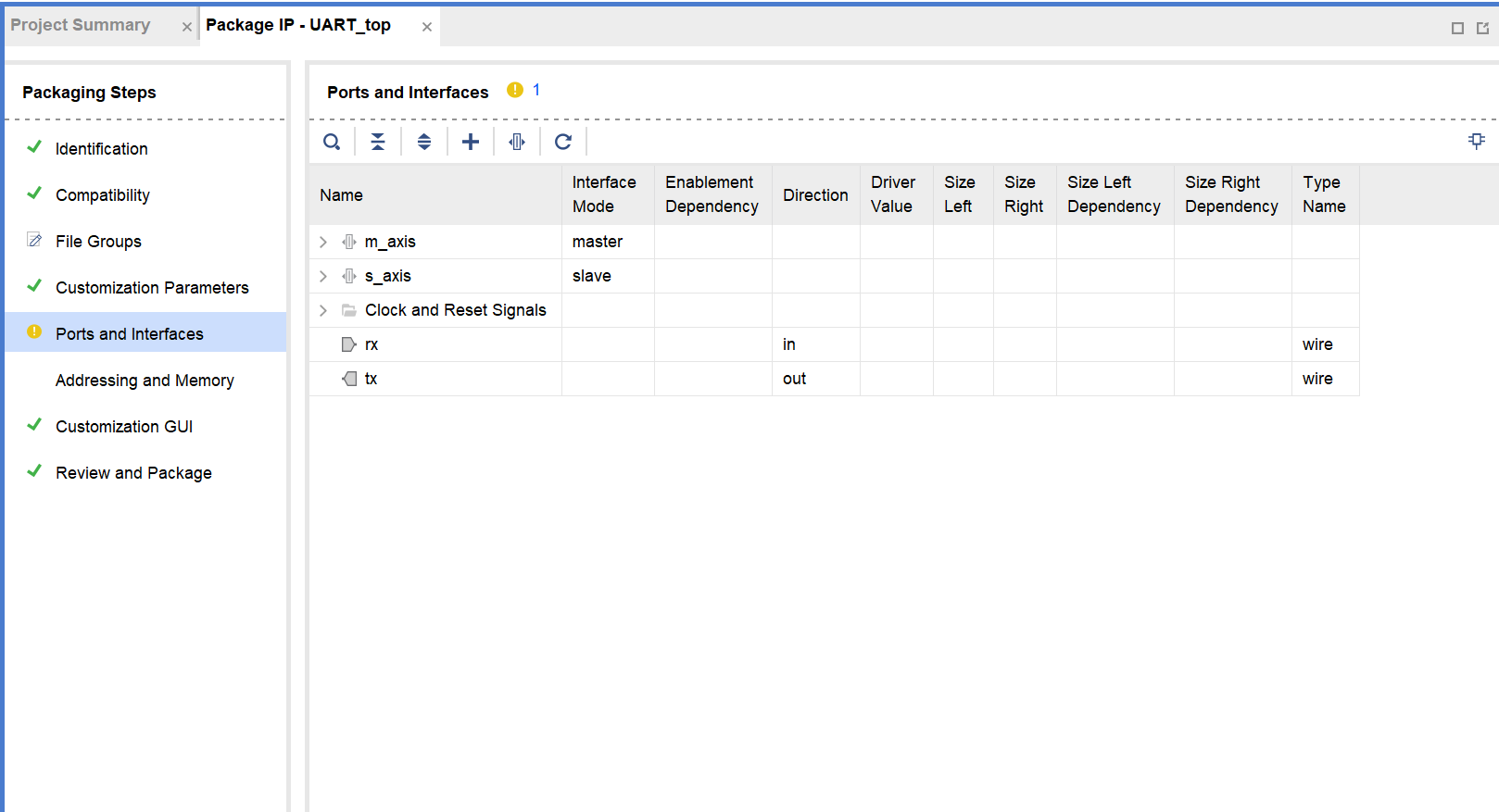

在图 7 的 Ports and Interfaces 界面可以调整接口,甚至可以使用 xilinx 官方的接口进行定义。选中所需要整合为接口的管脚,然后对其右键,选择 auto infer interface 即可选择需要的接口对选中的管脚进行定义。

图 7

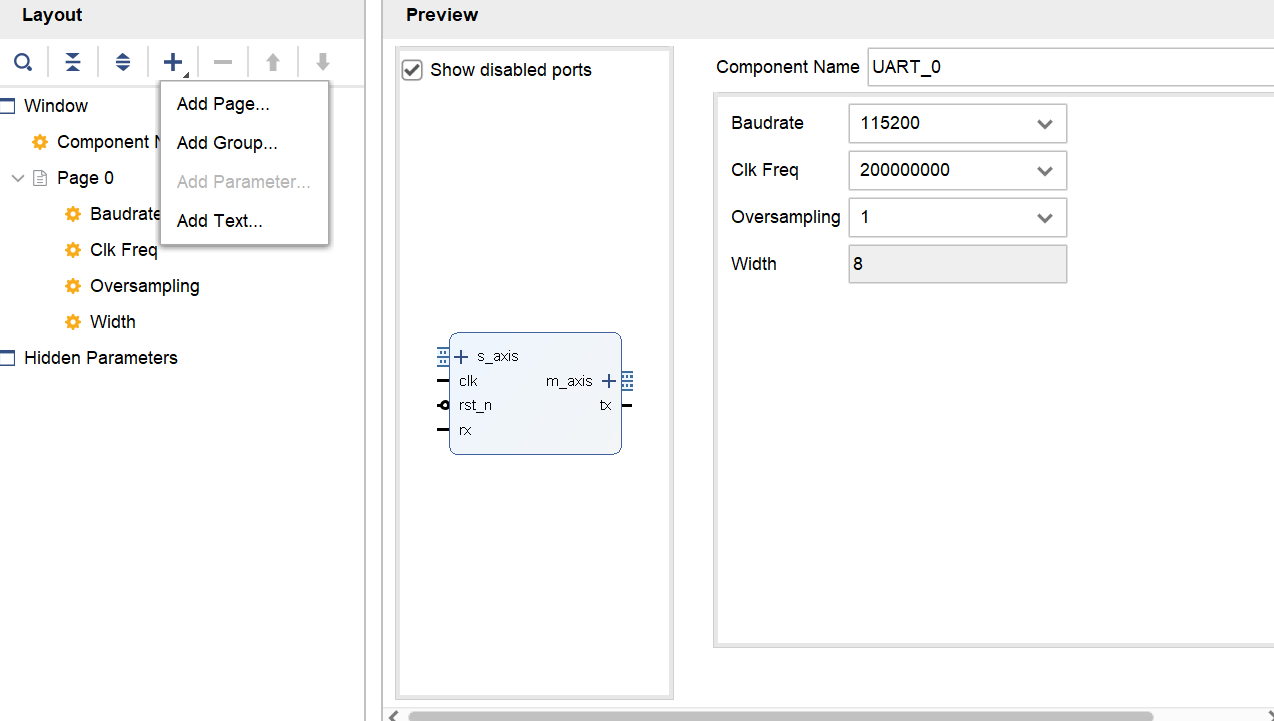

在目前的工程里,暂时不需要用到地址和内存部分,可以直接到 customization GUI 界面看自己 IP 的 GUI,在这里可以对接口进行分组、排序以及添加一些文本注释。

图 8

4. 完成后就可以进入 Review and Package 界面,点击 Package IP 进行封装。IP 封装完成后会存在与 IP Catalog 中,在此可以对其进行调用(图 9)。

图 9

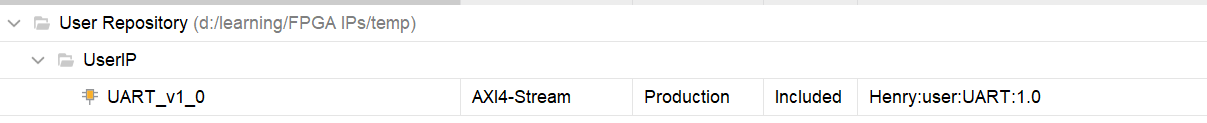

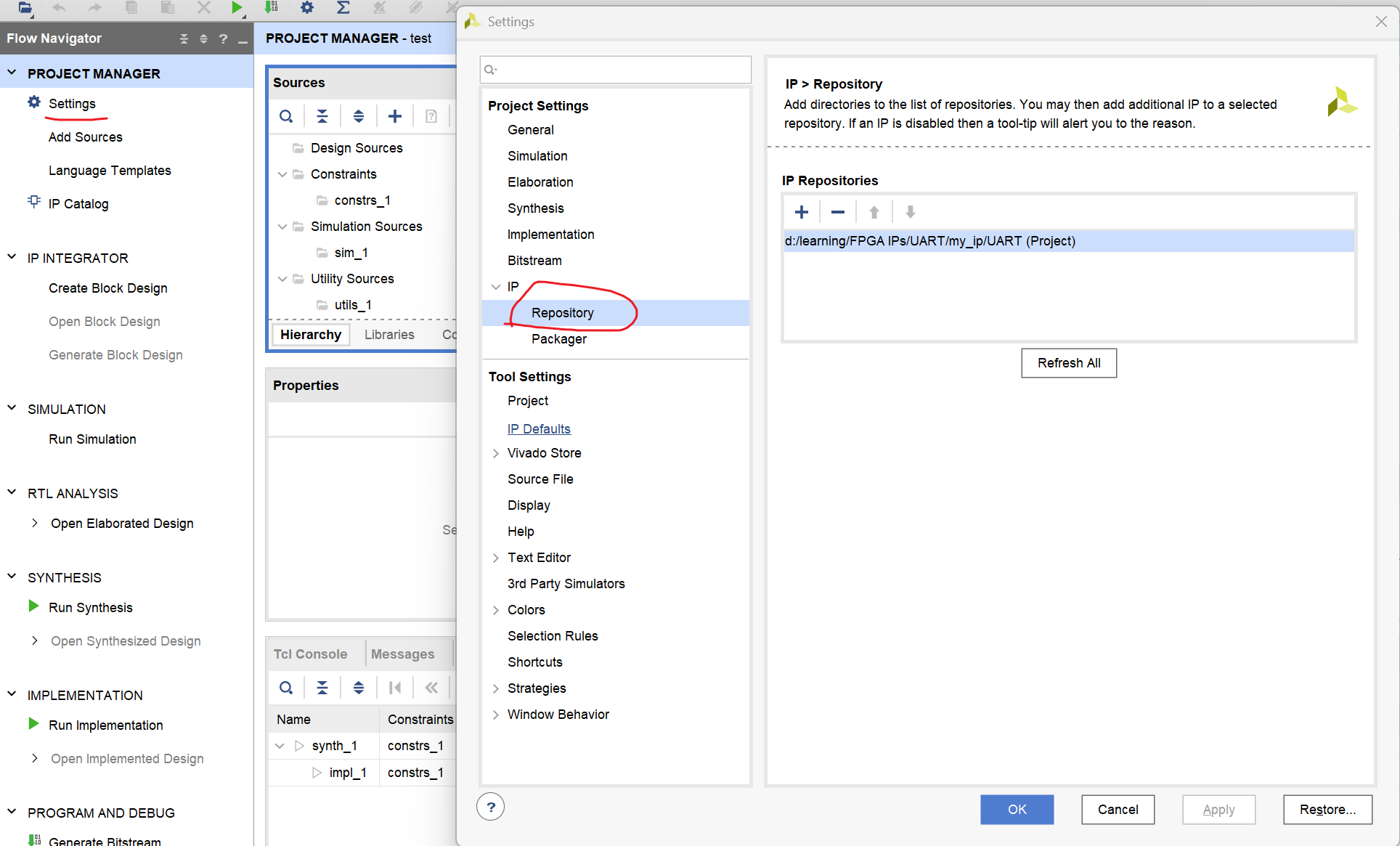

3.导入IP核

在新的工程里想使用 IP 核需要导入 IP 核,在新的工程里点 settings->IP->Repository,点击加号选择相应目录即可添加 IP 核

默认评论

Halo系统提供的评论